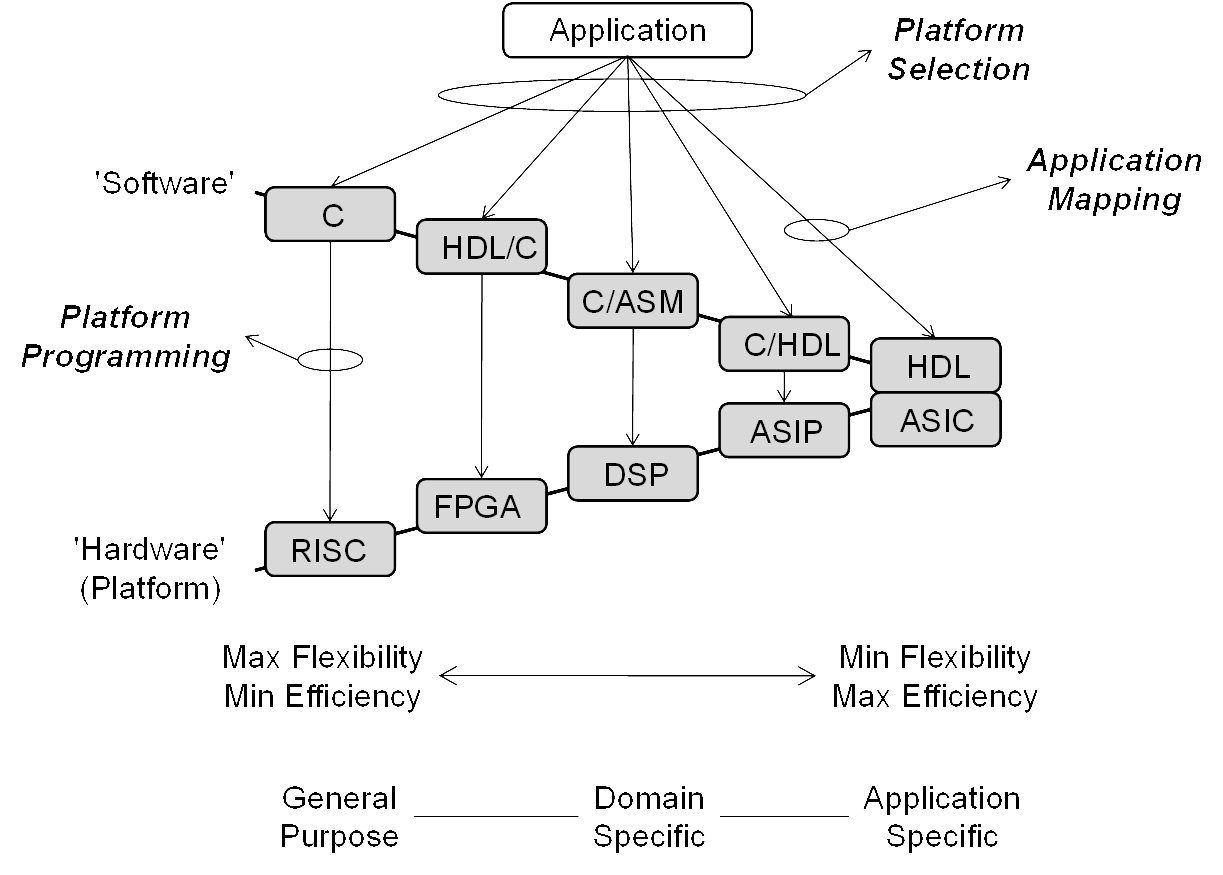

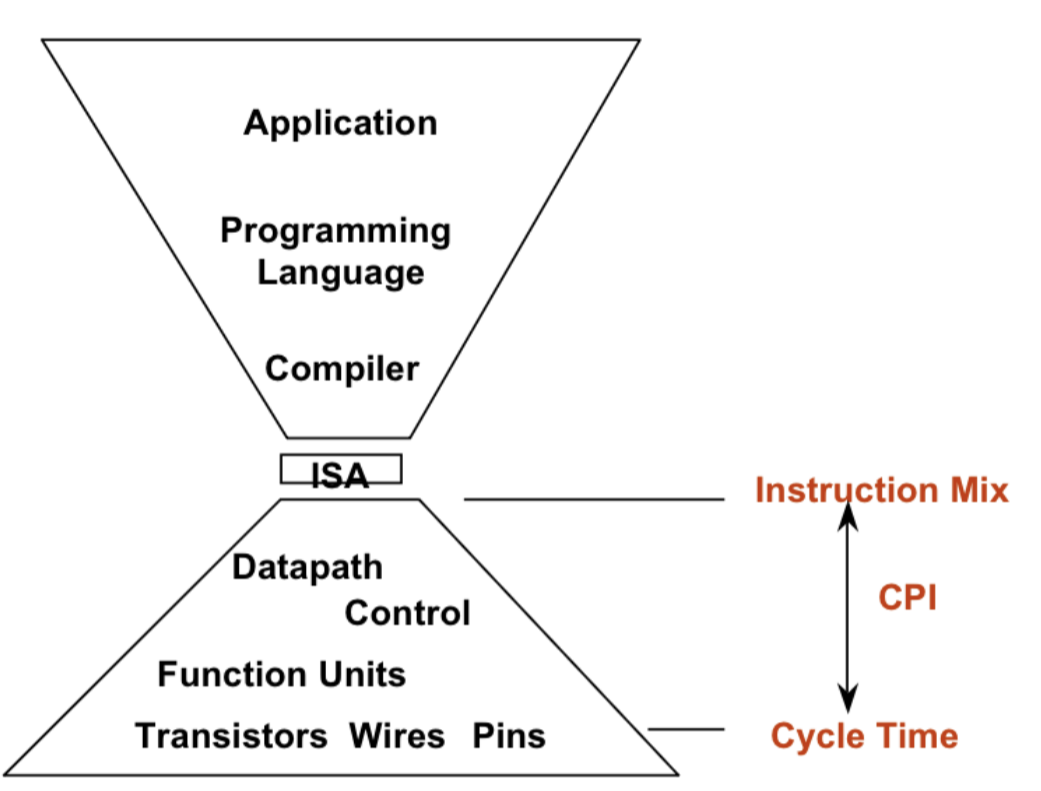

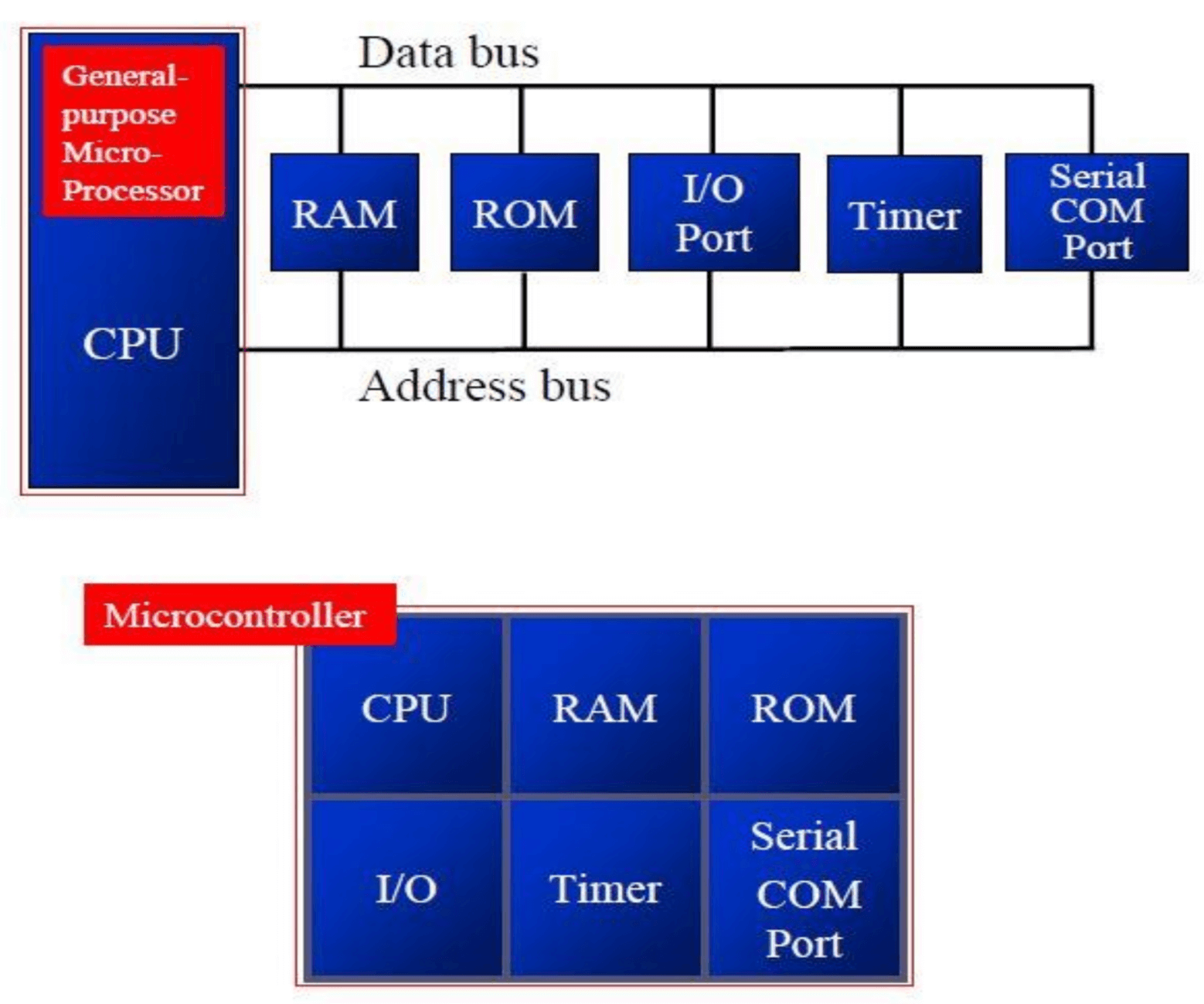

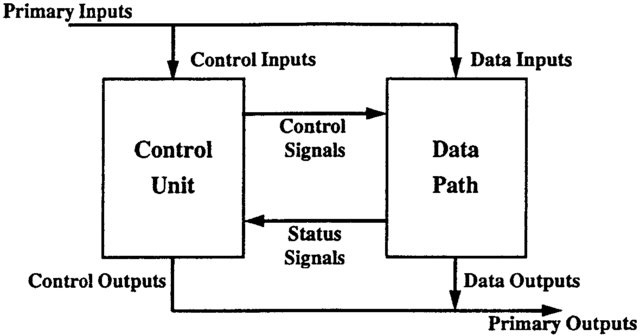

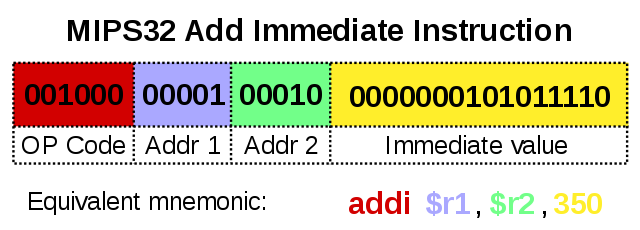

# Архитектура компьютера ## Лекция 7 ## Универсальный процессор. <br/> Машина фон Неймана Пенской А.В., 2026 --- ## Информационный процессор <div class="row"><div class="col"> <dl> <dt> Информационный процессор </dt> <dd> система (электрическая, механическая или биологическая), которая принимает информацию (последовательность символов или состояний) в одной форме и обрабатывает (преобразует) ее в другую форму. </dd> </dl> Например: исходный сигнал в статистику, посредством алгоритмического процесса. </div><div class="col">  Информационный процессор включает: 1. ввод 1. процессор 1. хранилище 1. вывод </div></div> ---- ### Универсальный процессор Позволяет решать широкий круг задач, настройка которых производится после производства "по месту" или в run-time. Примечания: 1. Универсальность $\neq$ полнота по Тьюрингу. 1. Теоретическая универсальность $\neq$ практическая универсальность. 1. Универсальность противоречит эффективности. 1. Современный процессор — совокупность программного и аппаратного обеспечения. <!-- ### Свойства универсального (программируемого) процессора --> Свойства: 1. 2-этапное производство (Hardware и Software) 1. Полнота по Тьюрингу 1. Отсутствие "серьезных" ограничений на "объём" программы 1. Изменяемость ПО --- ## Виды процессоров Гибкость и эффективности  <!-- .element: height="300px" --> <div class="row"><div class="col"> (1) Application-Specific Integrated Circuit (2) Coarse-Grained Reconfigurable Arrays <br/> (3) Field-Programmable Gate Array </div><div class="col"> (4) Digital Signal Processor <br/> (5) Graphics Processing Unit <br/> (6) **Central Processing Unit** <br/> </div></div> ---- ### Платформа и язык программирования  <!-- .element: height="550px" --> --- ### Архитектура процессора <dl> <dt> Архитектура процессора (architecture) </dt> <dd> то, как видит компьютер программист. Определена набором команд (язык), местом нахождения операндов (регистры и память) и вычислительными механизмами (кеш, прерывания...). </dd> </dl> -------------------- 1. Множество разных архитектур: - x86, MIPS, SPARC, ARM. - acc, cisc, risc, stack (элемент варианта лаб. 4) 1. Чтобы понять архитектуру, нужно знать её язык. 1. Слова в языке компьютера — "инструкции" или "команды". 1. Словарный запас — "система команд". ---- ### Микроархитектура процессора <dl> <dt> Микроархитектура процессора (microarchitecture) </dt> <dd> соединение простейших цифровых элементов в логические блоки, предназначенные для выполнения команд определенной архитектуры. </dd> </dl> -------------------- Примечания: 1. Описывает, как в процессоре расположены и соединены друг с другом регистры, АЛУ, конечные автоматы, блоки памяти, интерфейсы ввода-вывода и т.п. 1. У каждой архитектуры может быть много микроархитектур, обеспечивающих разное соотношение производительности, цены, сложности, технической эстетики. Они смогут выполнять одни и те же программы. 1. Если ISA и микроархитектура отличаются на уровне MoC — обычно требуется уровень виртуализации (ПО, аппаратура. транслятор...). ---- #### Система команд (ISA) <div class="row"><div class="col"> <dl> <dt> Система команд процессора </dt> <dd> (Instruction Set Architecture — ISA) абстрактная модель процессора, формирующая интерфейс взаимодействия между программным обеспечением и процессором. </dd> </dl> Производительность, энергопотребление и задержки часто не рассматриваются. <dl> <dt> Машинное слово </dt> <dd> фрагмент данных фиксированного размера, обрабатываемый как единое целое процессором. </dd> </dl> </div><div class="col"> 1. типы данных, 1. модель памяти, система и методы адресации, 1. набор инструкций, 1. механизмы обработки прерываний и исключений, 1. методы ввода и вывода.  <!-- .element: height="300px" --> </div></div> Notes: ECE C61 Computer Architecture Lecture 3 – Instruction Set - [Meltdown and Spectre](https://meltdownattack.com) - [Edward A. Lee Modeling in Engineering and Science](https://cacm.acm.org/magazines/2019/1/233519-modeling-in-engineering-and-science/fulltext) ---- #### Разнообразие систем команд Примеры разных команд (утрировано): 1. Действие над памятью/регистрами (фон Нейман): $\longrightarrow$ - произвольной сложности и длины (CISC), - фиксированного формата (RISC). 1. Действие без указания обрабатываемых данных (стековый). 1. Управляющие сигналы процессора под видом команды (NISC). 1. Группа команд под видом одной команды (VLIW). 1. Действие над шиной данных (TTA). 1. Команды без последовательного исполнения (редукционные). 1. Система команд из одной команды (URISC). 1. Управляющие сигналы процессоров под видом команды (NITTA). Notes: слишком много ссылок в будущее, надо как-то упростить. --- ## Машина фон Неймана <div class="row"><div class="col"> 1. Развитие машины Тьюринга. Ключевые отличия: - лента заменена на Random-Access Memory (RAM); - инструкции и данные объединены. 1. Призвана быть максимально простой в реализации и производстве. 1. Процедурное программирование и ООП — тот же принцип. </div><div class="col">  </div></div> ---- ### Машина фон Неймана. Особенности 1. Использование двоичного кодирования. - Встречается троичное и двоично-десятичное кодирование. 1. Программное управление. Команды выполняются последовательно. - Последовательность и порядок сегодня условны. 1. Память компьютера однородно хранит данные и программы. - Однородность спорна. 1. Ячейки памяти компьютера имеют адреса. Random-Access Memory. - Адрес не сводится к целому числу сегодня. - Память не является пассивным элементом компьютера. 1. Возможность условного перехода. - И перехода по иным причинам. ---- <div class="row"><div class="col"> #### Машина фон Неймана. Окружение <dl> <dt> [Микро]процессор </dt> <dd> цифровая схема, которая выполняет операции с внешним источником данных (обычно памятью или потоком данных). </dd> </dl> <dl> <dt> [Микро]контроллер </dt> <dd> микросхема, предназначенная для управления электронными устройствами. </dd> <dd> Типичный микроконтроллер сочетает функции процессора и периферийных устройств, содержит ОЗУ и (или) ПЗУ. </dd> </dl> </div><div class="col">  <dl> <dt> Оперативная память (память) </dt> <dd> обычно часть компьютерной памяти, в которой хранится выполняемый машинный код, а также входные, выходные и промежуточные данные. </dd> </dl> </div></div> ---- #### Машина фон Неймана. Control Unit и DataPath <div class="row"><div class="col"> <dl> <dt> Control Unit </dt> <dd> компонент центрального процессора (CPU), управляющий работой процессора. CU часто использует двоичный декодер для преобразования закодированных инструкций в управляющие сигналы, координирующие работу остальных блоков. </dd> </dl> <dl> <dt> Datapath </dt> <dd> АЛУ, набор регистров и внутренние шины CPU, по которым данные перемещаются между ними. </dd> </dl> Компоненты модели лаб. 4 </div><div class="col">   </div></div> ---- #### Машина фон Неймана. Виды инструкций <div class="row"><div class="col"> 1. **Работа с памятью**: запись констант, копирование данных (память, регистры, порты I/O). 2. **Арифметические, логические и битовые** операции (int, float). 3. **Управляющие операции**: безусловный, условный и косвенный переходы, вызов и возврат из подпрограмм. 4. **Инструкции сопроцессоров**: - Загрузка и выгрузка данных. - Управление сопроцессором. </div><div class="col">  - `OP Code` — код операции. - `Addr 1/2` — номера регистров общего назначения. - `Immediate value` — непосредственное значение. - `$r1` `<- $r2 + 350` - При переполнении: - `$r1` — без изменений, - установить флаг overflow. </div></div> ---- #### Машина фон Неймана. Роль машинного слова Единица данных, которая выбрана естественной для данной архитектуры процессора. 1. Может быть адресована в памяти. 1. Передаётся по шине между памятью и процессором за один раз. 1. Является стандартной единицей обрабатываемой информацией. 1. Связанные вопросы: - формат инструкции; - форматы данных; - форматы адресов. --- ### Машина фон Неймана. Пример программы Программа — последовательность инструкций в памяти компьютера. - Последовательное исполнение инструкций с условными переходами. - Инструкции изменяют состояние процессора. - Последовательная модель вычислений. > Пример написан на x86-подобном CISC ассемблере — для иллюстрации концепции фон Неймана. ```text | Address | Mnemonic | Comment | | ------- | -------------- | ----------------------------------------- | | 0400 | MOV CX, [0500] | CX <- [0500] | | 0404 | MOV AX, 0001 | AX <- 0001 | | 0407 | MOV DX, 0000 | DX <- 0000 | | 040A | MUL CX | DX:AX <- AX * CX | | 040C | LOOP 040A | Go To [040A] | | | | till CX->00 (CX <- CX - 1 on each step) | | 0410 | MOV [0600], AX | [0600]<-AX | | 0414 | MOV [0601], DX | [0601]<-DX | | 0418 | HLT | Stop Execution | ``` - Алгоритм расчёта факториала: - Входные данные по адресу `0500` равны 3. - Результат сохранить по адресам `[0600, 0601]`. ---- #### Машина фон Неймана. Пример трассы процесса Трасса процесса — очерёдность смены состояний процессора. ```text 1. {AX: x, CX: x, DX: x} Выполняется 0400 | MOV CX, [0500] 2. {AX: x, CX: 3, DX: x} Выполняется 0404 | MOV AX, 0001 3. {AX: 1, CX: 3, DX: x} Выполняется 0407 | MOV DX, 0000 3.1. {AX: 1, CX: 3, DX: 0} Выполняется 040A | MUL CX 3.2. {AX: 3, CX: 3, DX: 0} Выполняется 040C | LOOP 040A CX не равно 0, переходим 040A. 3.3. {AX: 3, CX: 2, DX: 0} Выполняется 040A | MUL CX 3.4. {AX: 6, CX: 2, DX: 0} Выполняется 040C | LOOP 040A, CX не равно 0, переходим 040A 3.5. {AX: 6, CX: 1, DX: 0} Выполняется 040A | MUL CX 3.6. {AX: 6, CX: 1, DX: 0} Выполняется 040C | LOOP 040A, после декремента CX равно 0, выполняем следующую инструкцию. 4. {AX: 6, CX: 0, DX: 0} Выполняется 0410 | MOV [0600], AX 5. {AX: 6, CX: 0, DX: 0} Выполняется 0414 | MOV [0601], DX 6. Выполняется 0418 | HLT, Остановить выполнение ``` Регистры `AX`, `DX`, `CX` — брошены в "случайном" состоянии. ---- ### Машина фон Неймана. Практика 1. В чистом виде практически не встречается. 1. Влияние на индустрию — трудно переоценить. 1. Элементы архитектуры присутствуют в подавляющем большинстве процессоров и средств разработки. 1. Структурное программирование, ООП — наследие фон Неймана. 1. Ловушка обратной совместимости. > Can Programming be Liberated from the von Neumann Style? — Backus, John. 1977 Turing Award Lecture <!-- Попытка сделать эскиз современного процессора:  --> --- ### Машина фон Неймана. Вариации 1. Память команд и данных: Принстонская и Гарвардская архитектуры - Типы данных, адресные пространства, машинные слова, теги 1. Принцип работы с данными в DataPath - Accumulator, Register-to-Register, Register-to-Memory, Memory-to-Memory, Stack Architectures 1. "Мощность" системы команд: CISC, RISC - Количество операндов (0, 1, 2...) - Кодирование инструкций - Принципы построения Control Unit 1. Адресация операндов: ```text - подразумеваемая (OpCode) - укороченная (часть адреса) - непосредственная (hardcode) - косвенная (адрес в ячейке) - прямая (числом) - адресация слов переменной длины - относительная (`addr + base`) - стековая - автоинкрементная и автодекрементная ``` Кроме того: ввод-вывод, параллелизм, иерархия памяти, и т.п.